Verilog 中 报错的全面解析

Verilog 是一种硬件描述语言,广泛应用于数字电路设计和仿真,在实际编程过程中,开发者经常会遇到各种编译错误,其中 是一个常见的问题,本文将全面探讨这一错误的可能原因、解决方法以及相关的常见问题和解答。

一、常见原因及解决方法

1、缺少

原因:每个模块必须以 如果忘记添加,或者添加了多余的,都会导致语法错误。

解决方法:检查代码,确保每个模块都有且只有一个对应的 语句。

2、拼写错误

原因: 关键字拼写错误,如写成、 等。

解决方法:仔细检查代码中的拼写,确保所有关键字都正确无误。

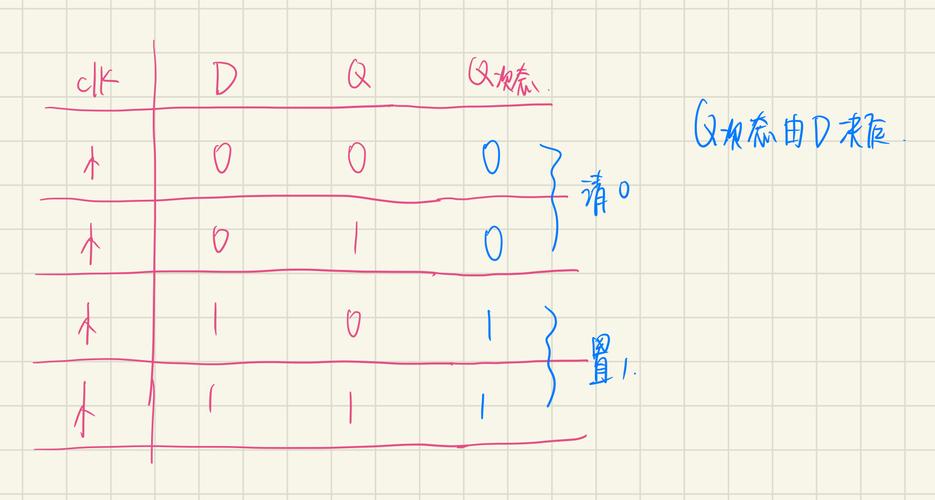

3、语法错误

原因:代码中可能存在其他语法错误,导致编译器无法正确识别,缺少必要的括号、分号等。

解决方法:检查整个模块的代码,确保没有遗漏任何必要的符号。

4、注释错误

原因:不正确的注释形式可能导致编译器误判,使用了单行注释 而不是多行注释。

解决方法:确保使用正确的注释格式。

5、模块嵌套错误

原因:在一个模块内部定义了另一个模块,但没有正确闭合。

解决方法:确保每个模块都是独立的,并且正确闭合。

6、未匹配的块

原因:块的开始和结束不匹配,如 没有对应的。

解决方法:检查每个块的开始和结束是否匹配。

二、相关FAQs

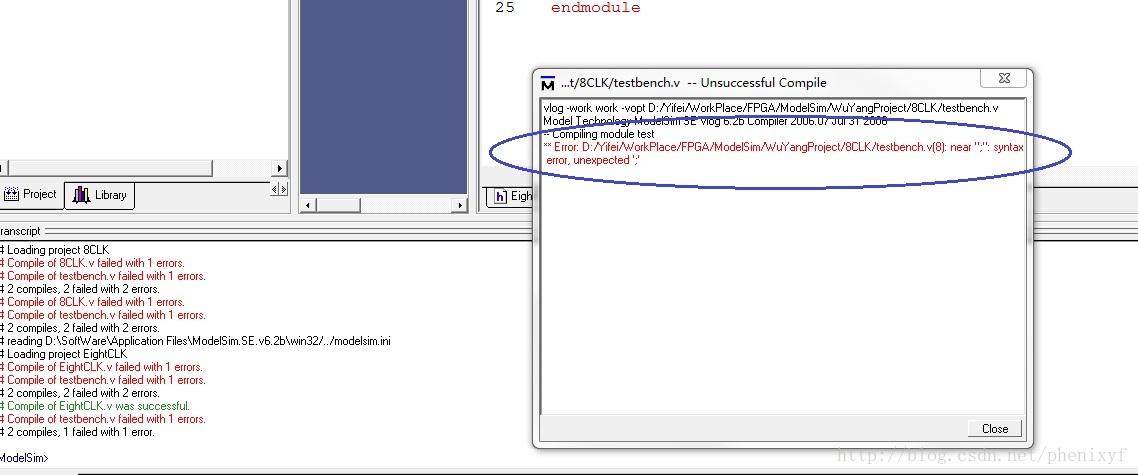

1、为什么会出现 错误?

回答:这个错误通常表示在 Verilog 代码中缺少 关键字,可能是由于模块未正确闭合,或者存在拼写错误或语法错误导致的,检查代码,确保每个模块都有相应的 语句,并且没有其他语法错误。

2、如何解决 Verilog 中的语法错误?

回答:仔细阅读错误信息,定位出错的具体位置,检查该位置附近的代码,确保所有括号、分号、关键字等都正确无误,可以使用 Verilog 编辑器或验证工具来帮助查找和修复错误,确保代码风格一致,避免拼写错误和不一致的命名。

错误通常是由于模块未正确闭合、拼写错误或语法错误导致的,通过仔细检查代码并确保每个模块都有相应的 语句,可以有效解决这一问题,掌握一些基本的调试技巧也能提高编程效率和代码质量。

到此这篇codependence no more中文(code note)的文章就介绍到这了,更多相关内容请继续浏览下面的相关推荐文章,希望大家都能在编程的领域有一番成就!版权声明:

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。

如若内容造成侵权、违法违规、事实不符,请将相关资料发送至xkadmin@xkablog.com进行投诉反馈,一经查实,立即处理!

转载请注明出处,原文链接:https://www.xkablog.com/rfx/50638.html