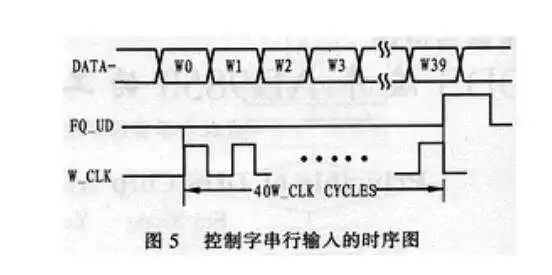

AD9850有40位控制字,32位用于频率控制,5位用于相位控制。1位用于电源休眠(Powerdown)控制,2位用于选择工作方式。这40位控制字可通过并行方式或串行方式输入到AD9850,图4是控制字并行输入的控制时序图,在并行装入方式中,通过8位总线A0…D7将可数据输入到寄存器,在重复5次之后再在FQ-UD上升沿把40位数据从输入寄存器装入到频率/相位数据寄存器(更新DDS输出频率和相位),同时把地址指针复位到第一个输入寄存器。接着在W-CLK的上升沿装入8位数据,并把指针指向下一个输入寄存器,连续5个W-CLK上升沿后,W-CLK的边沿就不再起作用,直到复位信号或FQ-UD上升沿把地址指针复位到第一个寄存器。在串行输入方式,W-CLK上升沿把25引脚的一位数据串行移入,当移动40位后,用一个FQ-UD脉冲即可更新输出频率和相位。图5是相应的控制字串行输入的控制时序图。

AD9850的复位(RESET)信号为高电平有效,且脉冲宽度不小于5个参考时钟周期。AD9850的参考时钟频率一般远高于单片机的时钟频率,因此AD9850的复位(RESET)端可与单片机的复位端直接相连。

值得一提的是:用于选择工作方式的两个控制位,无论并行还是串行最好都写成00,并行时的10、01和串行时的10、01、11都是工厂测试用的保留控制字,不慎使用可能导致难以预料的后果。

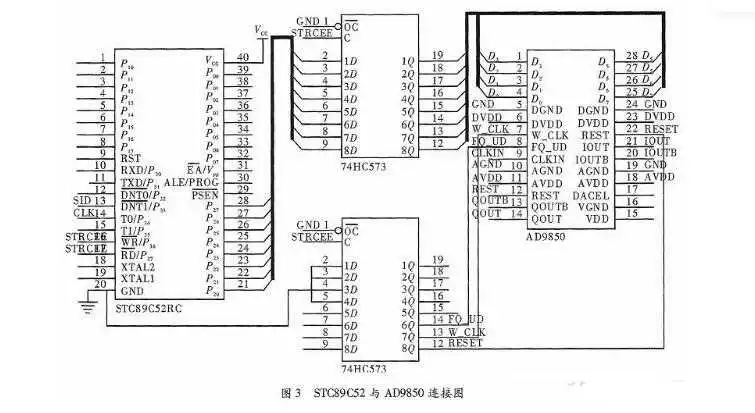

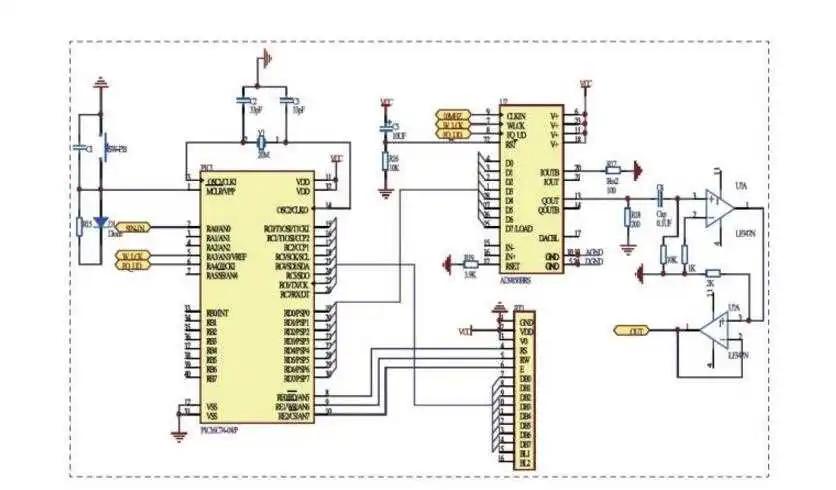

AD9850的40位频率/相位控制字可通过并行或串行两种方式送入器件。选用并行传输方式,充分发挥芯片AD9850的高速性能。在并行方式下连续输入 5次数据,每次输入8位(1 Byte),将40位频率/相位控制字送入器件。系统中,单片机通过数据锁存器和控制锁存器来实现对AD9850模块的控制,数据锁存器打开时,控制锁存器关闭,此时传输数据;控制锁存器打开时,数据锁存器关闭,此时根据AD9850的时序对W_CLK、FQ_UD、RESET执行相应的操作。单片机 89C52控制AD9850工作连线图,如图3所示。

总线方式并行接口占用的单片机资源较少,而且本设计中信号发生器只是作为单片机控制模块的外围扩展模块之一,因此AD9850工作在控制字并行输入方式。此时,AD9850仅作为一扩展芯片只占用一个地址。其原理图如图4所示。

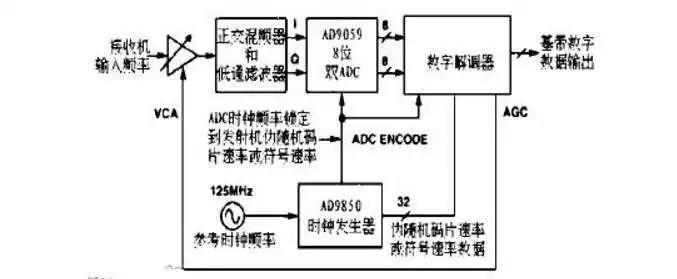

AD9850 时钟发生器在扩频接收器中的应用

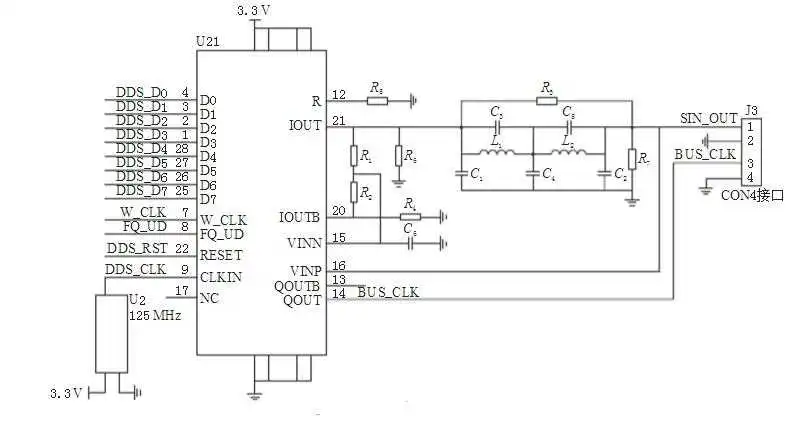

AD9850是美国AD公司生产的高集成度的DDS合成芯片。它采用32位相位累加器,截断成14位,输入正弦查询表,查询表输出截断成10位,输入到DAC。DAC输出两个互补的模拟电流,接到滤波器上。但是AD9850直接产生的信号幅度只有2V左右,而且是单极性的。而测试的时候需要的是双极性的正弦信号,因此DDS输出的信号还要经过隔直和放大。AD9850输出的信号经过RC高通滤波器,将直流分量滤除,输出交流信号,再经放大器放大,电压跟随,输出幅度适当、带载能力较强的信号源。电路如图所示。

版权声明:

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。

如若内容造成侵权、违法违规、事实不符,请将相关资料发送至xkadmin@xkablog.com进行投诉反馈,一经查实,立即处理!

转载请注明出处,原文链接:https://www.xkablog.com/jszy-gxgz/30313.html