计算机组成结构源于冯·诺伊曼计算机结构,该结构成为现代计算机系统发展的基础。冯·诺伊曼计算机结构将计算机硬件划分为5部分,包括:控制单元,运算单元,存储器,输入设备和输出设备。

其中控制单元和运算单元在现代计算机结构被集成为一体,封装为通常意义上的处理器;输入设备和输出设备则经常被设计者集成为一体,按照传输过程被划分为总线,接口和外部设备。

现代计算机硬件基本构成

现代计算机硬件基本构成

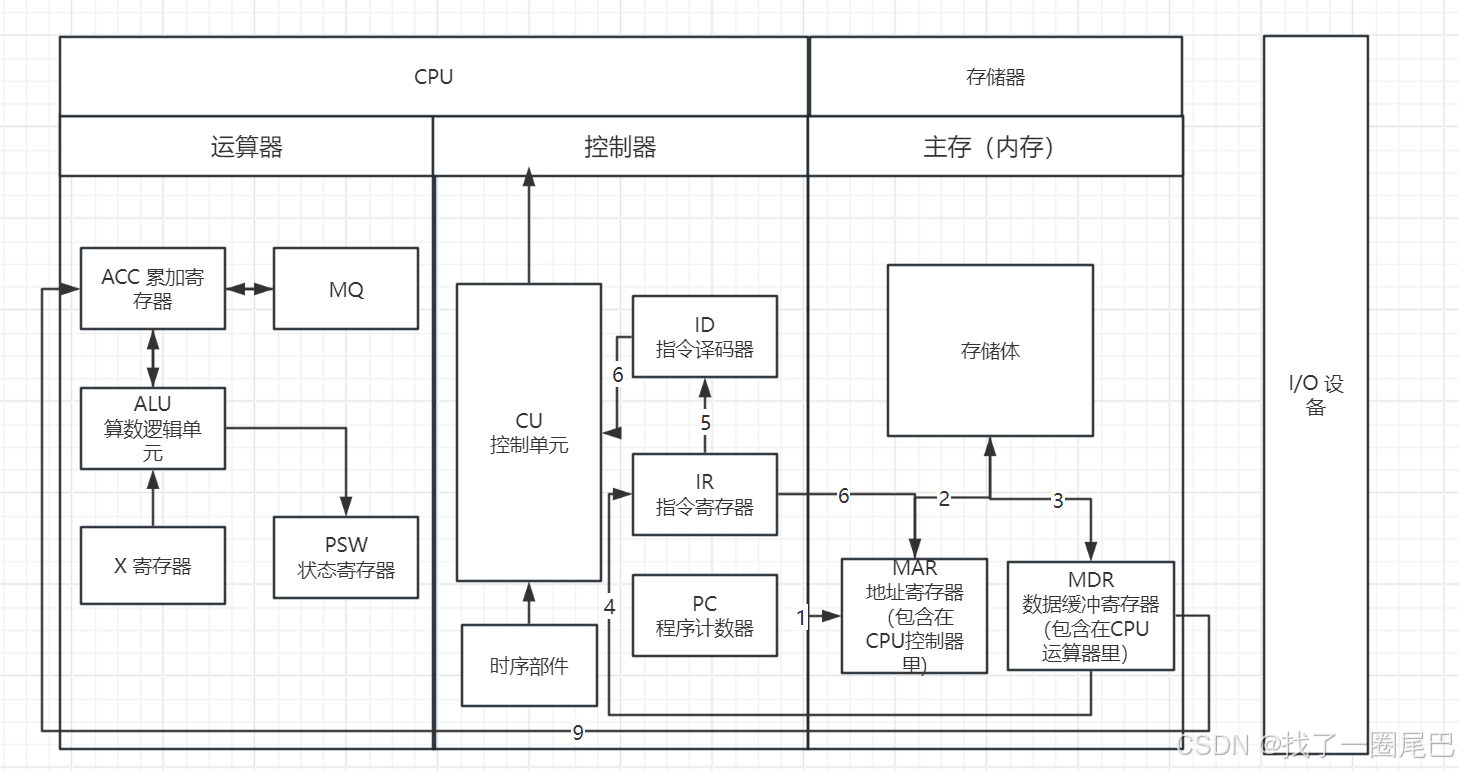

- 运算器

- 算数逻辑单元 ALU:数据的算术运算和逻辑运算

- 累加寄存器 AC/ACC: 通用寄存器,为ALU提供一个工作区,用来暂存数据

- 数据缓冲寄存器 DR: 写内存时,暂存指令和数据

- 状态寄存器 PSW:存状态标志与控制标志

- 控制器

- 程序计数器 PC :存储下一个要执行的指令

- 指令寄存器 IR:存储即将执行的指令

- 指令译码器 ID:对指令中的操作码字段进行分析解释

- 地址寄存器 AR:用来保存当前CPU 所访问的内存单元的地址

- 时序部件:提供时序控制信号

- CPU指令执行步骤:

- 取指: PC(程序计数器) ->AR (地址寄存器)->M(存储体) - >DR(数据缓冲寄存器) ->IR(指令寄存器)

- 分析:OP(指令操作码字段) ->ID (指令译码器)->CU (控制单元)

- 执行: AD(指令操作数地址码字段) ->AR(地址寄存器)->M(存储体) - >DR(数据缓冲寄存器) ->ACC (累加寄存器)

处理器作为计算机系统运算和控制的核心部件,经历了长期演化过程。

- 在位宽上由4位处理器发展到64位处理器;

- 在能力构成上从仅具有运算和控制功能发展到集成多级缓存,多种通信总线和接口;

- 在内核上从单核处理器发展为多核,异构多核和众核处理器等

- 专用处理器

- 图形处理器(GPU):GPU 是一种特殊类型的处理器,具有数百或数千个内核,经过优化可并行运行大量计算,因此近些年在深度学习和机器学习领域得到了广泛应用。

- 信号处理器(DSP):DSP 专用于实时的数字信号处理,通过采用饱和算法处理溢出问题,通过乘积累加运算提高矩阵运算的效率,以及为傅里叶变换设计专用指令等方法,在各类高速信号采集的设备中得到广泛应用。

- 现场可编程逻辑门阵列(FPGA):FPGA是一种可编程逻辑器件,它由大量的逻辑门、存储单元和可编程互连资源组成。与传统的固定功能集成电路(ASIC)不同,FPGA可以通过编程来实现特定的功能,而不需要进行物理电路的改变。通过编程和配置,FPGA可以实现特定的电路功能,满足不同应用场景的需求。

指令集

处理器的指令集按照其复杂程度可以分为复杂指令集(CISC) 与精简指令集 (RISC)两类。

CISC 以 Intel,AMD 的 x86CPU为代表;RISC 以 ARM 和 Power 为代表。除了由于历史原因而仍然存在的 CISC 结构外,RISC 已经成为计算机指令集发展的趋势,几乎所有后期出现的指令集均为 RISC 结构。

复杂指令集 CISC的特点

- 指令数量众多。指令系统拥有大量的指令,通常有 100-250 条。

- 指令使用频率相差悬殊。最常用的是一些比较简单的指令,仅占指令总数的20%,但在程序中出现的频率却占80%。大部分复杂指令很少使用。

- 支持多种寻址方式,5-20种。

- 变长的指令。指令的长度是不固定的,变长的指令增加指令译码电路的复杂性。

- 指令可以对主存单元的数据直接进行处理。典型的CISC 通常都有指令能够直接对主存单元中的数据进行处理,其执行速度比较慢。

- 以微程序控制为主。CISC 的指令系统很复杂,难以用硬布线逻辑(组合逻辑)电路实现控制器,通常采用微程序控制。

精简指令集 RISC的特点

- 指令数量少。优先选取使用频率最高的一些简单指令和一些常用指令,避免使用复杂指令。只提供了 LOAD(从存储器中读数)和 STORE(把数据写入存储器)两条指令对存储器操作,其余所有操作都在CPU 的寄存器之间进行。

- 指令的寻址方式少,通常只支持寄存器寻址方式,立即数寻址方式和相对寻址方式。

- 指令固定长度,指令格式种类少。因为RISC 指令数量少,格式少,相对简单,其指令长度固定,指令之间各字段的划分比较一致,译码相对容易。

- 以硬布线逻辑控制为主。为了提高操作的执行速度,通常采用硬布线逻辑来构建控制器。

- 单周期指令执行,采用流水线技术。很容易利用流水线技术,使得大部分指令都能在一个机器周期内完成。少数指令可能会需要多周期,例如:LOAD/STORE 指令因为需要访问存储器,其执行时间就会长一些。

- 优化的编译器:RISC 的精简指令集使编译工作简单化。因为指令长度固定,格式少,寻址方式少,编译时不必在具有相似功能的许多指令中进行选择,也不必为寻址方式的选择而费心,同时易于实现优化,从而可以生成高效率执行的机器代码。

- CPU中的通用寄存器数量多,一般在32个以上,有的可达上千个。

指令寻址方式

- 立即寻址:指令的地址字段不是操作数的地址,而是操作数本身。

- 寄存器寻址:指令给出的操作数地址是通用寄存器的编号,寄存器中存放的内容是操作数

- 直接寻址:在指令格式的地址字段中直接指出操作数在内存的地址

- 寄存器间接寻址:指令格式中操作数地址所指向的寄存器中存放的内容不是操作数,而是操作数的地址,通过该地址可在内存中找到操作数

- 相对寻址:把程序计数器PC 的内容加上指令格式中的形式地址来形成操作数的有效地址

- 速度:立即寻址 > 寄存器寻址 > 直接寻址 > 寄存器间接寻址

存储器是利用半导体,磁,光等介质制成用于存储数据的电子设备。如图所示为存储器的分类及划分层级

存储器详细分类

分类方式

存储类型

存储方式

按照与处理器的物理距离

片上缓存

在处理器核心中直接集成的缓存,一般为SRAM结构,实现数据的快速读取。它容量较小,一般为 16KB~512KB,按照不同的设计可能划分为一级或二级。

按照与处理器的物理距离

片外缓存

在处理器核心外的缓存,需要经过交换互联开关访问,一般也是由SRAM构成,容量较片上缓存略大,可以为256KB~4MB。按照层级被称为L2Cache 或 L3Cache,或者称为平台Cache。

按照与处理器的物理距离

主存(内存)

通常采用DRAM结构,以独立的部件/芯片存在,通过总线与处理器连接。DRAM依赖不断充电维持其中的数据,容量在数百MB至数十GB之间。

按照与处理器的物理距离

外存

可以是磁带,磁盘,光盘和各类Flash等介质器件,这类设备访问速度慢,单容量大,且在掉电后能够保持其数据。不同的介质类型容量及保存数据的年限都有所不同。

按照寻址方式分类

随机存储器 RAM

按照地址访问存储器的任一单元

主存

按照寻址方式分类

顺序存储器 SAM

访问时按顺序查找目标地址

磁带

按照寻址方式分类

直接存储器 DAM

按照数据块所在的位置访问

磁盘

按照寻址方式分类

按照内容进行访问

Cache

按照内部存储单元的工作原理

SRAM

不需要刷新电路即能保存它内部存储的数据。因此SRAM具有较高的性能,但是集成度较低,相同容量的DRAM内存可以设计为较小的体积,但是SRAM需要很大的体积,且功耗较大。

静态存储器

按照内部存储单元的工作原理

DRAM

只能将数据保持很短的时间。为了保持数据,DRAM使用电容存储,所以必须隔一段时间刷新一次,如果存储单元没有被刷新,存储的信息就会丢失。

动态存储器,最为常见的系统内存

高速缓冲寄存器(cache)

- cache 是一种介于主存和微处理器(CPU)之间的高速存储器,用于主存和CPU 之间的缓冲存储。其命中率必须很高,一般要达到90%~95%以上,才能使访问主存的速度跟得上CPU 的速度。在CPU 和 Cache 之间通常一次传送一个字块,字块的长度是一个主存周期内能调出的信息的长度。如果Cache 不命中,则用从主存中取到的字节代替Cache中较少访问过的字节,即同时送CPU 和 Cache,下次就可以从Cache 中读出需要的信息了。

- 在程序执行过程中,Cache 与主存的地址映像由硬件自动完成。

- 解决CPU 和主存之间的速度差异,避免CPU"空等“现象。

- 高速缓冲寄存器是存在于主存与CPU 之间的一级存储器,由静态存储芯片(SRAM)组成,容量比较小但速度比主存高得多,接近于CPU 的速度。

- Cache 通常保存着一份内存存储器中部分内容的副本,该内容是最近曾被CPU 使用过的数据和程序代码

主存与Cache 的地址映射方式

- 直接映像

- 主存中一块只能映射到Cache的特定块中;

- 将主存分区,每个区的第0页,放在Cache的第0页;每个区的第1页,放在Cache的第1页。

- 直接映像方式的优点是地址变换很简单,缺点是不灵活,块冲突率高。

- 全相联映像

- 主存的任何一块可以映射到Cache 中的任意一块

- 位置不受限制,十分灵活

- 其主要缺点是无法从主存块号中直接获得Cache的块号,变换比较复杂,速度比较慢

- 组相联映像

- 将主存分区,分组;每个区采用直接映像,每个区的第0页,放在Cache的第0页;每个区的第1页,放在Cache的第1页。每个组采用全相联映像。

- 各区中的某一块只能存入缓存的同组号的空间内,但组内各块地址之间可以任意存放。即从主存的组到Cache 的组之间采用直接映像方式,在两个对应的组内部采用全相联映像。

- 特点

- 距离CPU 比较近的位置可采用直接映像或者组相联映像;

- 距离CPU 比较远的位置可采用全相联映像;

Cache 的性能

- cache 的设计思想是在合理的成本下提高命中率;

- Cache 的平均访问时间为 :

- 影响 Cache 命中率的因素包括高速存储器的容量,存储单元组的大小,组数多少,地址联想比较法,替换算法,写操作处理方法,程序特性等,这些因素相互影响,没有关键影响因素。

Cache的写策略

- 写回法:当CPU对cache写命中时,只修改cache的内容不立即写入主存,只当此行被换出时才写回主存。这种策略使cache在CPU-主存之间,不仅在读方向而且在写方向上都起到高速缓存作用。

- 写直达法 :又称全写法,写透。是当cache写命中时,cache与主存同时发生写修改。

- 标记法:数据进入cache后,有效位置1,当cpu对该数据修改时,数据只写入主存并将该有效位置0.要从cache中读取数据时,要测试其有效位,若为1则直接从cache中取数,否则从主存中取数。

Cache 替换算法

- 随机算法

- 先进先出(FIFO)

- 近期最少使用(LRU)

- 最不经常使用页置换(LFU)

磁盘阵列

磁盘阵列是由多台磁盘存储器组成的一个快速,大容量,高可靠的外存子系统。现在常见的磁盘阵列称为廉价冗余磁盘阵列 RAID。

RAID机制中共分8个级别,RAID应用的主要技术有分块技术,交叉技术和重聚技术。

级别

说明

特点

RAID 0

无冗余和无校验的数据分块

具有最高的I/O性能和最高的磁盘空间利用率。

RAID 1

磁盘镜像阵列

它将数据完全一致的分别写到工作磁盘和镜像磁盘,磁盘空间利用率50%。

RAID 2

采用纠错海明码的磁盘阵列

大量数据传输时I/O性能较高,但不利于小批量数据传输,实际应用中很少使用。

RAID 3

采用位交叉奇偶校验码的磁盘阵列

读快,写慢,适用于大型文件且I/O不频繁的应用

RAID 4

采用块交叉奇偶校验码的磁盘阵列

适用于大型文件的读取

RAID 5

无独立校验盘的奇偶校验码磁盘阵列

没有独立校验盘,校验信息分布在组内所有盘上,对于大批量和小批量的数据的读写性能都很好。使用了独立存取技术,阵列中每一个磁盘都相互独立地操作,所以I/O请求可以并行处理。因此,该技术非常适用于I/O需求频繁的应用而不太适合于要求高数据传输率(大型文件)的应用。当有N块阵列盘时,用户空间为N-1块盘容量。

RAID 6

具有独立的数据硬盘与两个独立的分布式校验方案

该盘具有独立的数据访问通路,但其性能改进有限,价格却很昂贵。用户空间为N-2 块盘容量。

RAID 7

具有最优化的异步高I/O速率和高数据传输率的磁盘阵列

是对RAID 6的改进。完全可以理解为一个独立存储计算机,它自身带有操作系统和管理工具,完全可以独立运行。在这种阵列中的所有磁盘,都具有较高传输速度,有着优异的性能,是目前最高档次的磁盘阵列。

RAID 10

高可靠性与高性能的组合

利用了RAID 0极高的读写效率和RAID 1较高的数据保护和恢复能力,使RAID 10 成为了一种性价比较高的等级。

校验码

- 定义:是一种通过对数据进行运算得到的一段二进制码。它可以用于检测和校正数据传输或存储中的错误。

- 码距:

- 一个编码系统的码距就是整个编码系统中任意(所有)两个码字的最小距离

- 在一个码组内为了检测e个误码,要求最小码距应该满足

- 在一个码组内为了纠正t个误码,要求最小码距应该满足

- 同时纠错检错:

奇偶校验码

奇偶校验是最简单的一种校验码算法,它通过统计数据中二进制中 1 的个数,来判断数据中是否存在错误。

如果数据中1的个数为偶数,则校验位为0;

如果数据中1的个数为奇数,则校验位为1;

奇偶校验只能检测出奇数个错误位,无法检测出偶数个错误位。

海明码

在奇偶校验的基础上,加入分组校验。

- 校验位:

是校验位,因为

是校验位,因为 在二进制表示中只有一个 1,所以分组的时候只属于1 组。

在二进制表示中只有一个 1,所以分组的时候只属于1 组。 - 分组规则: 二进制数第一位是 1 为第一组,第二位是 1 为第二组,第三位是 1 为第三组...

- 规则:设数据位是n位,校验位是k位,则n和k必须满足以下关系:

循环冗余校验码(CRC)

CRC是一种广泛应用于数据传输和存储过程中的校验码算法。它通过对数据进行多项式除法来计算校验码。CRC算法具有良好的错误检测和纠正能力,常用于网络通信、存储系统等领域。

- 计算CRC校验码的方式:

- 化解多项式

-

- 信息码加0做模二除运算(不进位加法)

-

- 得到的余数即为校验码。最终的信息位+ 校验码位为:101111100

总线(Bus)是指计算机部件间遵循某一特定协议实现数据交换的形式,即以一种特定格式按照规定的控制逻辑实现部件间的数据传输。

分类方式

类型

详细

备注

所处的位置划分

内部总线

用于各类芯片内部互连

也成为片上总线,片内总线

系统总线

常被称为局部总线

外部总线

计算机板和外部设备之间,或计算机系统之间互联的总线

又被称为通信总线

按总线功能划分

地址总线

用来传送地址信息

数据总线

用来传送数据信息

控制总线

用来传送各种控制信号

总线中数据线的多少

并行总线

多条双向数据线,有传输延迟,适合近距离连接。

适用于系统总线,主要包括PCI,PCIe和ATA(IDE)等;

串行总线

一条双向数据线或两条单向数据线;速率不高,但适合长距离连接。

适用于通信总线,主要包括USB,SATA,CAN,RS-232,RS-485,RapidIO和以太网等;

接口指同一计算机不同功能层之间的通信规则。对于总线而言,一种总线可能存在多种接口。常见的接口包括:

- 显示类接口(HDMI,DVI和VGA等)

- 音频输入输出类接口(TRS,RCA,XLR等)

- 网络类接口(RJ45,FC等)

- PS/2接口

- USB接口

- SATA接口

- LPT打印接口

- RS-232接口

- 非标准接口

- 离散量接口

- A/D转换接口

外部设备也称为外围设备,是计算机的非必要设备。现代计算机的外部设备种类日益丰富,包括所有的输入输出设备以及部分存储设备(即外存)。随着人们日益增长的物质需求,还会有更多形态各异,功能多样的外部设备产生。各型外部设备虽然种类多样,但都是通过接口实现与计算机主体的连接,并通过指令,数据实现预期的功能。

到此这篇进程控制块包含哪些信息类型(进程控制块有哪些组成)的文章就介绍到这了,更多相关内容请继续浏览下面的相关推荐文章,希望大家都能在编程的领域有一番成就!版权声明:

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。

如若内容造成侵权、违法违规、事实不符,请将相关资料发送至xkadmin@xkablog.com进行投诉反馈,一经查实,立即处理!

转载请注明出处,原文链接:https://www.xkablog.com/bcyy/67908.html